Sau phần giới thiệu công nghệ Chiplet ở kỳ trước, bài viết kỳ này sẽ khái quát về cuộc đua giữa các ông lớn trong ngành bán dẫn, qua đó thảo luận liệu Việt Nam có thể tham gia vào mảng đóng gói tiên tiến này không?

Intel, gã khổng lồ ngủ quên đã thức dậy?

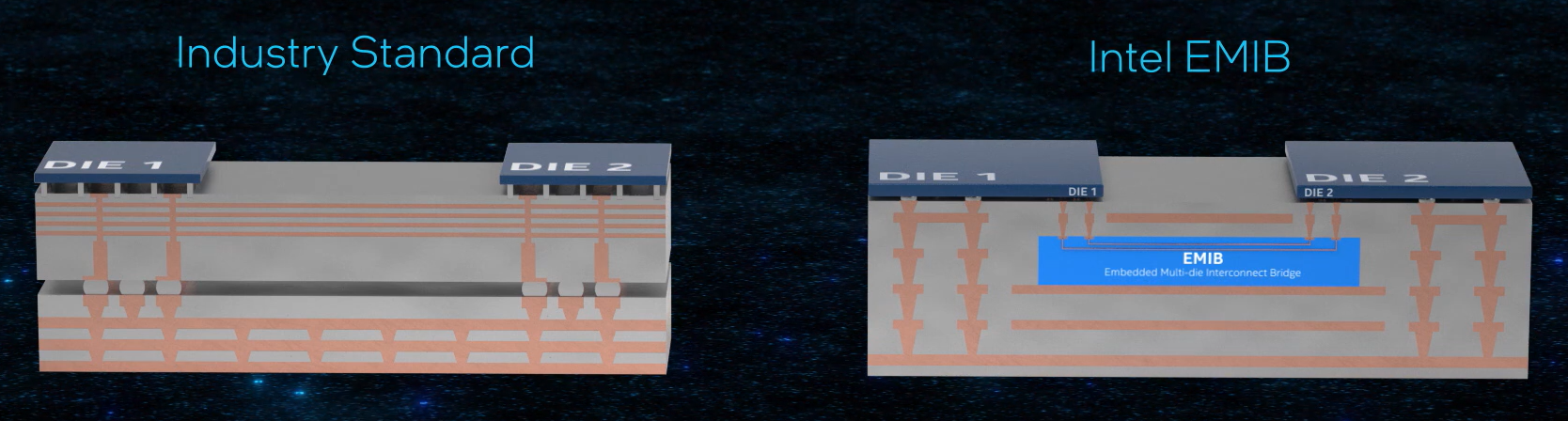

Năm 2014 Intel đưa ra khái niệm EMIB (Embedded Multi-Die Interconnect Bridge), giải pháp của Intel là sử dụng một dạng kiểu “ổ cắm” (socket) tiêu chuẩn, đảm nhận nhiệm vụ làm lớp kết nối giữa các chiplet với nhau thay vì sử dụng tấm nền silic (interposer) thông thường làm nhiệm vụ kết nối giữa các chiplet trước khi đặt lên khung (package substrate).

Cách thức sử dụng tầm nền truyền thống sẽ có nhược điểm kích thước của tấm nền bị phụ thuộc vào số lượng chiplet làm cho khả năng tùy chỉnh thiết kế sẽ bị hạn chế, kèm theo đó là chi phí sẽ cao hơn.

Intel đưa thông số kỹ thuật, bộ thư viện thiết kế, quy trình mẫu, và các quy định cần tuân thủ khi sản xuất của “ổ cắm” để các nhà cung cấp chiplet dễ dàng phát triển sao cho khi ghép lại với nhau thì đảm bảo mọi thứ hoạt động cùng nhau về tốc độ truyền nhận dữ liệu cũng như kiểm soát được nhiệt và nhiễu.

Ý tưởng này khá thú vị vì có thể tích hợp bao nhiêu chiplet cũng được, dễ dàng và nhanh chóng, quy trình đóng gói ít tốn kém. Nhưng khi tấm nền được tối ưu, nhỏ hơn, mỏng hơn thì hiệu quả tản nhiệt khi tích hợp nhiều chiplet sẽ trở thành vấn đề nghiêm trọng. Khi đó cần giải pháp bổ sung để làm mát. Đôi khi việc này lại khá tốn kém.

Theo một báo cáo mới của Intel, phương pháp đóng gói 3D của họ cho phép sử dụng chip hoặc wafer từ các xưởng đúc khác nhau, băng thông kết nối được xác định bởi “via” làm bằng đồng với khoảng cách giữa các via là 9µm, có thể thu hẹp khoảng cách giữa các via xuống 3µm trong thế hệ tiếp theo.

Intel cũng tuyên bố rằng công nghệ sắp xếp tiên tiến này của họ có thể đảm bảo nếu với các chiplet đã được kiểm chứng hoạt động tốt thì yield đạt tới 97% khi tiến hành kiểm định sau đóng gói.

Intel cũng đã và đang nghiên cứu một phương pháp tốt hơn trong việc cung cấp điện năng cho các bóng bán dẫn. Khi mật độ bóng bán dẫn và số lượng lớp dây dẫn tín hiệu kim loại tăng lên, dây dẫn cung cấp điện năng từ trên xuống xen kẽ với các dây dẫn tín hiệu kim loại là giải pháp không tối ưu trong việc cung cấp đủ điện năng tới tất cả bóng bán dẫn và có thể làm cho vấn đề nhiễu trở nên nghiêm trọng hơn. Điều này càng ngày càng trở nên khó giải quyết với các nút tiến trình tiên tiến, do chất điện môi và dây dẫn mỏng hơn (ngày càng nhạy cảm với nhiễu).

Intel đã công bố kế hoạch cung cấp công nghệ cho phép cung cấp điện năng từ mặt sau của chip (PowerVia) trong năm nay, việc này sẽ giải quyết vấn để nêu trên và giải phóng thêm nhiều không gian cho các kết nối dây dẫn tín hiệu, làm tăng mật độ tích hợp bóng bán dẫn.

Thách thức của việc khoan lỗ qua lớp đế mà không làm hỏng cấu trúc chip là một thách thức không dễ vượt qua và rất đáng mừng là Intel đã có cách để vượt qua nó. Tuy nhiên, TSMC cũng cho biết họ có kế hoạch cung cấp công nghệ cho phép cung cấp điện năng từ mặt sau (tương tự Intel) lên A16 vào năm 2026/2027. Và Samsung dường như cũng có kế hoạch tương tự, cung cấp nó ở tiến trình 2nm (SF2Z).

Samsung, người tiên phong nhưng không gặp thời ?

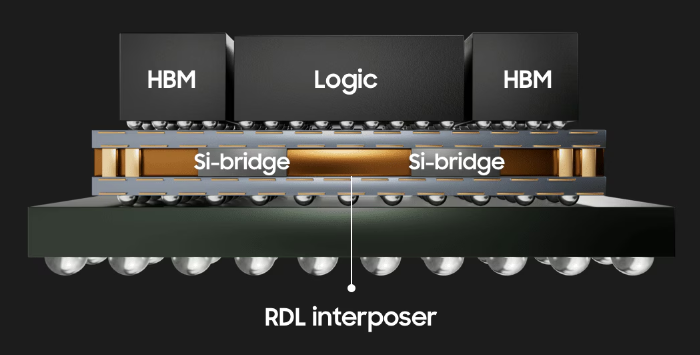

Tương tự với EMIB của Intel, Samsung đưa ra khái niệm I-Cube có cùng nguyên tắc hoạt động là các “cầu nối” (bridges) liên kết giữa các chiplet. Sự khác biệt là một số chức năng của cầu nối được nhúng ngay vào lớp RDL (redistribution layers – những lớp kim loại được thêm lên bề mặt của wafer nhằm định tuyến lại các kết nối tới vị trí được bố trí trước của chân tín hiệu vào/ra – I/O pins.)

Cách tiếp cận này có vẻ khá hữu dụng khi xây dựng một IC phức tạp lên tới con số hàng trăm lõi tính toán (CPU) mô phỏng mạng neuron đi kèm là các bộ nhớ băng thông rộng (HBM), các khối điều khiển giao tiếp với NPU và thông qua một hệ thống tín hiệu độc lập (off-chip bus) giao tiếp với chiplet khác.

Điểm hấp dẫn của phương pháp này là khả năng tản nhiệt. Với logic tách biệt khỏi các chức năng khác, nhiệt có thể được dẫn ra khỏi các đế được xếp chồng qua chất nền hoặc bất kỳ mặt tiếp xúc nào khác. Ngoài ra, Samsung cũng chú ý xây dựng liên minh riêng trong đó phân công các công ty quy mô nhỏ cung cấp chuyên biệt chiplet cho các thị trường cụ thể.

Hiện nay công nghệ chiplet vẫn đang chủ yếu phục vụ cho nhu cầu tùy chỉnh cho các ứng dụng cụ thể chứ chưa phải là một thị trường thương mại có tính hàng loạt khi một chiplet có thể hoạt động tốt trong nhiều trường hợp sử dụng khác nhau.

Thêm nữa, hiện tại vẫn chưa ngã ngũ việc nên theo một chuẩn chung kết nối giữa các chiplet (UCIe) hay theo phương án “cầu nối”; và làm sao để các chiplet tới từ các đối tác khác nhau (yếu tố nhiệt, nhiễu, lão hóa không nhất quán) được tích hợp trong cùng một “bao bì” có thể hoạt động nhịp nhàng dưới các tải tính toán và điều kiện vận hành khác nhau. Điều này là cũng khó dự đoán ngay cả bằng việc sử dụng các công cụ mô phỏng tốt nhất, vì sẽ không bao giờ có đầy đủ dữ liệu đầu vào.

Do đó, xu thế chủ đạo hiện nay vẫn là chiplet cần phải được cung cấp từ một nguồn, nơi chúng ta có toàn quyền kiểm soát hệ thống thay vì có thể sử dụng chiplet từ các nguồn khác nhau. Và một khi điều này được chứng minh là hiệu quả thì các liên minh riêng lẻ của ba xưởng đúc chính sẽ ngày càng được mở rộng.

Các thông tin gần đây cho thấy Samsung đã bắt đầu có kế hoạch cho phép xếp chồng các DRAM lên trên lớp logic. Nhớ lại vào năm 2011, Samsung và Micron đã cùng nhau phát triển công nghệ tương tự là đóng gói DRAM lên trên một lớp logic (HMC – Hybrid Memory Cube). Tuy nhiên sau đó HBM giành chiến thắng, JEDEC biến nó thành một tiêu chuẩn còn HMC gần như là biến mất. Có lẽ lúc đó không phải là thời điểm đúng của HMC.

Ở lần thứ hai của cách tiếp cận này, Samsung cung cấp HBM tùy chỉnh với bộ nhớ có kích thước phù hợp với khối lượng công việc hoặc loại dữ liệu cụ thể và một số quá trình xử lý có thể được thực hiện bên trong module bộ nhớ để có ít dữ liệu hơn phải di chuyển cho phép khả năng đọc/ghi và di chuyển dữ liệu qua lại nhanh hơn giữa bộ nhớ và bộ vi xử lý. Điều này sẽ có tác động lớn tới cải thiện hiệu suất và công suất tiêu thụ năng lượng.

TSMC – liệu có thể tiếp tục giữ vững vị trí ngôi vương?

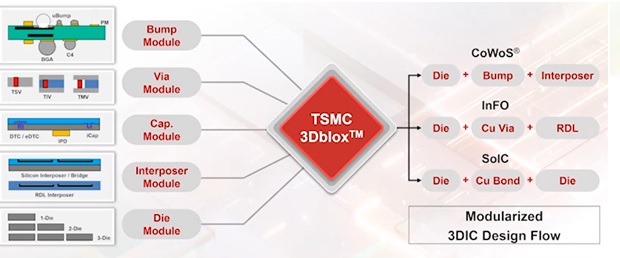

Với TSMC, cùng là cách tiếp cận “cầu nối” như Intel và Samsung, nhưng họ đã thử nghiệm các phương án khác nhau, bao gồm cả phương án cầu nối nhúng ở RDL và không nhúng ở RDL. TSMC gọi nó là chip được xếp chồng trên tấm wafer chồng lên trên đế, CoWoS (Chip-on-Wafer-on-Substrate) với các kết nối rất ngắn.

Thực tế thì TSMC đang tích cực tạo ra bộ quy tắc đóng gói tiên tiến kèm các ví dụ tham khảo cụ thể, giống như cách TSMC tạo ra các quy trình cho hầu hết mọi ứng dụng để các nhà thiết kế sử dụng trong thời gian vừa qua.

Và khi khách hàng càng ngày càng mong muốn có các giải pháp cho phép khả năng tùy chỉnh với độ tin cậy cao trong khi các công cụ thiết kế hiện nay vẫn còn khá thiếu nhất quán và gần như khó cho phép xảy ra việc tái sử dụng các chiplet trong các thiết kế khác nhau, TSMC giới thiệu một hệ thống cú pháp gọi là 3Dblox, dựa trên việc module hóa các thành tố mang tính đặc thù của kỹ thuật chiplet, cho phép khách hàng có thể linh hoạt hơn trong các lựa chọn thiết kế của mình.

Hình ảnh minh họa về 3Dblox - Nguồn: TSMC

Nói thêm là, Samsung cũng giới thiệu ngôn ngữ 3DCODE vào tháng 12/2023, cả Samsung và TSMC đều tuyên bố ngôn ngữ của họ mới là tiêu chuẩn nhưng gần như chắc chắn không có khả năng những ngôn ngữ này có thể được sử dụng bên ngoài hệ sinh thái (liên minh) của riêng họ. Riêng Intel là không yêu cầu cần một ngôn ngữ bởi mọi quy tắc được chuẩn hóa qua thông số kỹ thuật của “ổ cắm”, dường như nó là một cách tiếp cận đơn giản hơn với các nhà phát triển theo trường phái chiplet.

Trong thực tế, CoWoS của TSMC đã được NVIDIA và AMD sử dụng cho đóng gói các chip AI của họ. TSMC cũng khẳng định rằng phương pháp của họ cho phép kết nối nhanh hơn và ngắn hơn so với các phương pháp đóng gói 3D khác. Một báo cáo cho biết Apple cũng sẽ sử dụng công nghệ đóng gói tiên tiến SoIC của TSMC trong khi AMD sẽ mở rộng việc sử dụng phương pháp này.

Theo Nikkei, TSMC đang sản xuất khoảng 90% chip tiên tiến nhất trên toàn cầu. TSMC cũng có nhiều kinh nghiệm nhất về đóng gói tiên tiến so với bất kỳ xưởng đúc nào và có hệ sinh thái lớn nhất và rộng nhất. Và thật không quá khi nói rằng, sức mạnh thực sự của TSMC là khả năng cung cấp bộ phát triển tiện dụng bao phủ hầu hết các quy trình đóng gói tiên tiến nhất.

TSMC tập trung nhiều vào việc xây dựng hệ sinh thái và không ngừng mở rộng các dịch vụ của mình cho tới hiện tại đã chứng minh là một hướng đi thành công. Trong bối cảnh ngành công nghiệp chip ngày càng phức tạp và đa dạng đến mức không một công ty nào có thể làm được mọi thứ, hệ sinh thái đóng vai trò rất quan trọng. Câu hỏi đặt ra trong tương lai sẽ là các hệ sinh thái đó thực sự hoàn thiện và sẽ lớn đến mức nào?

Kết luận

Gần đây chúng ta chứng kiến những khoản đầu tư lớn chưa từng có vào nghiên cứu, xây dựng nhà máy sản xuất bán dẫn, sẽ cần thêm thời gian để có thể biết được tác động của nó như thế nào.

Nhưng rõ ràng là thay vì chỉ có một lộ trình công nghiệp duy nhất như trước đây, ba nhà “đúc chip” hàng đầu – Intel, Samsung và TSMC, mới đang là những người quyết định cách thức để đến được nút tiến trình công nghệ tiếp theo.

Tuy tất cả cùng đang hướng đến một mục đích chung là thu nhỏ kích thước bóng bán dẫn (tới kích thước Angstrom), chiplet và cung cấp các công cụ/công nghệ hỗ trợ nhằm xây dựng hệ sinh thái lớn hơn và đa dạng hơn, nhưng họ ngày càng hoàn thiện con đường của riêng mình, tạo ra các tiền đề về phương pháp khác nhau cho những cải tiến rất đáng kể vể hiệu suất cũng như đảm bảo quản trị tối ưu hệ sinh thái làm cho thời gian giao hàng được nhanh hơn.

Chính khả năng cung cấp các giải pháp có ý nghĩa đối với khách hàng, nhanh chóng và hiệu quả mới là chìa khóa thực sự, nhưng mặt khác chắc chắn nó cũng đang là động lực chính thúc đẩy các công nghệ mới như quang học, các vật liệu mới và điện toán siêu lạnh (cryogenic computing) [5]./.

Nguyễn Thanh Yên (Tổng Giám đốc Công ty Vi mạch CoAsia SEMI Việt Nam) dịch và tổng hợp

____________

Tài liệu tham khảo

[1] https://www.chiphistory.org/505-moore-s-law-101-the-math-and-innovation-economics-behind-it

[2] https://irds.ieee.org/

[3] https://ictvietnam.vn/tich-hop-khong-dong-nhat-co-hoi-cho-phat-trien-linh-vuc-vi-mach-ban-dan-tai-viet-nam-23564.html

[4] https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs/

[5] https://semiengineering.com/intel-vs-samsung-vs-tsmc/

Đăng số 1309 (số 37/2024) KH&PT