Chiplet, một phương pháp mới để đóng gói chip, cho phép nhiều bóng bán dẫn được đóng gói trong một khối nhỏ gọn với chi phí rẻ hơn, giúp tiết kiệm chi phí và tối ưu hóa hiệu suất đang trở thành một xu hướng mới trong thiết kế và sản xuất vi mạch.

Bài tổng quan sau đây sẽ khái quát về xu hướng mới này và cuộc đua giữa các ông lớn trong ngành bán dẫn, qua đó để thảo luận liệu Việt Nam có thể tham gia mảng đóng gói tiên tiến này không?

*

Kể từ năm 1965, khi Gordon E. Moore [1] công bố quan sát có tính dự báo về tốc độ thu nhỏ kích thước bóng bán dẫn rằng số lượng linh kiện bán dẫn mà chúng ta có thể ép vào một mạch tích hợp sẽ tăng gấp đôi mỗi năm, thì một thời gian dài sau đó, gần như mọi thứ liên quan tới ngành công nghiệp bán dẫn đều được tóm gọn trong bản báo cáo cập nhật của tổ chức ITRS (International Technology Roadmap for Semiconductors). Có thể nói khi đó chỉ có một lộ trình công nghệ duy nhất quyết định cách thức để đến được những nút tiến trình công nghệ tiếp theo.

Đến năm 2015, khi ITRS kết thúc sứ mệnh lịch sử của mình để chuyển sang trang sử mới IRDS (International Roadmap for Devices and Systems) [2], trong các bản báo cáo cuối cùng của mình, tuy vẫn có những dự báo về những nút tiến trình công nghệ ở các kích thước tiếp theo như: 8/7 nm vào năm 2019; 4/3nm vào năm 2024, … nhưng có nhiều hơn những báo cáo nói về tích hợp không đồng nhất [3], sơ đồ đóng gói 2.5D/3D, việc sử dụng vật liệu bán dẫn mới [4]. Đó là thời điểm định luật Moore nổi tiếng bắt đầu được diễn giải ở những chiều không gian mới.

Cho đến hiện nay, trong thị trường sản xuất chip, sự quan tâm gần như không còn dồn hết vào việc xưởng đúc nào đang sản xuất chip tại nút tiến trình công nghệ nhỏ nhất ở kích thước nào nữa mà đã có sự dịch chuyển sang việc ai đang đặt hàng đóng gói chip có hàng chục chiplet bên trong cho một ứng dụng chuyên biệt nào đó và xưởng đúc nào có khả năng đáp ứng được nhu cầu đó; hoặc hiệu suất trên mỗi watt là bao nhiêu; hay thậm chí có một số ứng dụng chẳng còn màng tới yếu tố công suất nữa mà yêu cầu bắt buộc kết hợp càng nhiều tính năng càng tốt trong một “bao bì” duy nhất.

Rõ ràng là cuộc đua giữa các hãng đúc chip đang trở nên phức tạp hơn trước đây rất nhiều, đã xuất hiện những ngã ba thay vì sẽ chỉ đi trên một lộ trình duy nhất. Trong tất cả sự phức tạp đó là hình ảnh của một thuật ngữ quan trọng, chiplet, thứ đã, đang và sẽ tạo ra thêm nhiều ngã ba nữa trên con đường phát triển của công nghệ bán dẫn trong tương lai.

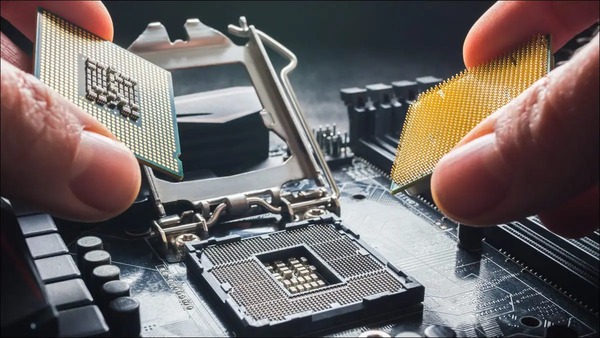

Chiplet có thể hiểu chính là miếng lõi bán dẫn của những vi mạch điện tử (IC) rời rạc chưa được đóng gói. Trước đây, sau khi trải qua quá trình thiết kế, chế tạo, các miếng lõi bán dẫn này được cắt ra từ tấm wafer - miếng silicon mỏng, vật liệu nền để sản xuất vi mạch, đặt lên một bộ khung chắc chắn và tín hiệu được kết nối tới chân bên ngoài IC tạo thành những linh kiện rời rạc hoạt động theo một chức năng định sẵn (hình ảnh những con chip màu đen kích thước chỉ vài milimet vuông với nhiều “chân cẳng” màu trắng tua tủa ở xung quanh quen thuộc trong các bo mạch điện tử).

Khái niệm chiplet gắn liền với kỹ thuật tích hợp không đồng nhất, nghĩa là chúng ta có thể đặt các chiplet có chức năng khác nhau kết hợp lại trên cùng một bộ khung, đóng gói lại trong cùng một “bao bì” thành một IC có chức năng mới. (SiP – System in Package)

Nếu theo cách thức truyền thống, khi IC cần bổ sung một chức năng mới thì chúng ta cần trải qua quá trình từ đầu bằng công đoạn thiết kế, chế tạo, đóng gói, kiểm tra, rồi mới có thể sản xuất hàng loạt, quá trình này rất mất thời gian. Công nghiệp bán dẫn đã có một lịch sử phát triển tương đối dài, vô cùng nhiều linh kiện rời rạc đã được tối ưu, kiểm chứng về chức năng và quan trọng là luôn trong trạng thái sẵn sàng sản xuất hàng loạt. Đôi khi nhu cầu bổ sung chức năng mới chỉ là “tìm” và “ghép” cái đã có sẵn (LEGO), việc này sẽ rút ngắn thời gian giao hàng và đáp ứng hoàn hảo các yêu cầu thiết kế tùy chỉnh ngày càng trở nên phổ biến của khách hàng.

Thoạt nhiên, điều này nghe có vẻ tầm thường nhưng nếu đưa được những thiết kế dành riêng đáp ứng nhu cầu của từng lĩnh vực một cách nhanh chóng (nhanh hơn nhiều phương thức truyền thống) ra thị trường thì đó lại là lợi thế cạnh tranh có tính quyết định nhất và chính nó đang làm thay đổi cơ bản về cách thức thiết kế, sản xuất và đóng gói chip trong gần một thập niên vừa qua.

Thời gian qua đã chứng minh việc đưa công nghệ đóng gói tiên tiến mới vào thực tế đã mở ra cánh cửa cho một loạt các lựa chọn cạnh tranh có quy mô và tác động rộng lớn hơn trước gấp nhiều lần. Trước đây, các nhà sản xuất chip, các nhà cung cấp thiết bị và các công ty EDA (Electronic Design Automation) chuyên cung cấp phần mềm và công nghệ để tự động hóa quy trình thiết kế vi mạch và chip là người xác định lộ trình cho thế hệ chip tiếp theo.

Nhưng chiplet đã mở ra một phương thức mới để khách hàng cuối có thể tự do tùy chỉnh và quyết định thế hệ chip tiếp theo là gì. Điều này có được là bởi vì số lượng tính năng có thể tích hợp trong một bao bì (SiP) gần như là không có giới hạn (có thể mở rộng theo chiều ngang, chiều dọc, hoặc cả hai) trong khi “chip theo cách truyền thống” đang tiến tới giới hạn số lượng tính năng có thể tích hợp trong một chip.

Đồng thời, ở một khía cạnh khác, trí tuệ nhân tạo/học máy (AI/ML) đòi hỏi sức mạnh xử lý dữ liệu rất lớn, đòi hỏi các bóng bán dẫn nhỏ hơn có hiệu suất năng lượng lớn hơn cần đảm bảo có được sự đồng nhất cao cho phép tạo ra nhiều hơn các mảng phần tử xử lý và cấu trúc bóng bán dẫn cần được cải tiến để ngăn chặn dòng rỏ rỉ. Điều này đòi hỏi trong các hệ thống chiplet phức tạp gồm nhiều loại bộ xử lý vẫn cần một số loại chuyên dụng được phát triển tại các nút quy trình tiên tiến với ưu điểm hiệu suất năng lượng cao và cho phép tích hợp nhiều bóng bán dẫn hơn trên một đơn vị diện tích.

Gần đây, cả ba xưởng đúc lớn hiện nay đều đã công bố kế hoạch tiến tới mức kích thước Angstrom, tương đương 1×10-10 mét, hay 0,1 nanomet: Intel có kế hoạch giới thiệu 18A trong năm 2024, tiếp theo đó là 14A; TSMC thì thêm vào tiến trình A16 trong lộ trình tới năm 2027 của mình, còn Samsung sẽ đẩy lên thẳng 14 angstrom (SF1.4) cũng vào năm 2027 và dường như sẽ bỏ qua 18/16 angstrom.

Nhìn từ nút tiến trình công nghê, cả ba xưởng đúc đều đi trên cùng một con đường, và việc dẫn đầu trong việc đưa ra thị trường các nút tiến trình công nghệ mới vẫn có giá trị, nhưng đó mới chỉ là một phần của bức tranh lớn hơn nhiều.

Tiến bộ công nghệ giờ đây không còn chỉ giới hạn ở kích thước trong nút tiến trình nữa, trọng tâm ngày càng tập trung vào độ trễ và hiệu suất trên mỗi watt trong phạm vi một ứng dụng xử lý tổng thể những luồng dữ liệu cụ thể. Việc xếp chồng các bóng bán dẫn này lên trên các bóng bán dẫn khác là cách tốt nhất tiếp theo và trong một số trường hợp thậm chí còn tốt hơn cả di chuyển electron qua dây dẫn đi từ đầu này tới đầu kia trên một mặt phẳng rộng vì đường dẫn tín hiệu dọc có thể ngắn hơn ngang.

Chiplet tự bản thân nó đang mang lại những lợi ích rõ ràng, chúng độc lập với các nút tiến trình công nghệ. Nhưng việc tìm ra cách ghép các mảnh lại với nhau với sơ đồ kiến trúc giống LEGO lại rất phức tạp và đòi hỏi những nỗ lực liên tục và lớn lao của cả hệ sinh thái quy mô toàn cầu. Các thách thức chủ yếu để phát triển Chiplet là:

- Vấn đề đồng bộ hóa dữ liệu trong xử lý, lưu trữ và truy xuất, chỉ một phép tính bị trễ hoặc không đồng bộ với các phép tính khác có thể dẫn đến những hậu quả nghiêm trọng do những rủi ro tiềm ẩn trong bối cảnh của những ứng dụng quy mô tính toán, tương tác dữ liệu vô cùng lớn, thậm chí nguy hiểm đe dọa đến mức độ an toàn khi hiện tại vẫn chưa có bất cứ phương pháp mô phỏng nào có thể mô phỏng được hết các trường hợp trong thực tế.

- Trong cuộc chạy đua giữa ba xưởng đúc hiện nay, có đến hơn một phần ba các thiết kế tiên tiến đang nằm trong tay các khách hàng cuối là các gã khổng lồ công nghệ như Google, Microsoft, Tesla, ... (các chip được phát triển cho các công ty này có thể sẽ không được bán ra thị trường đại chúng và đi kèm theo đó là sự cạnh tranh ngày càng gay gắt trong việc nắm giữ bí quyết công nghệ) thì việc đơn giản hóa quy trình thiết kế, đặc biệt là với các thiết kế cần sự hợp tác chặt chẽ của các bên là một nỗ lực phi thường.

Đứng trước những cơ hội to lớn về AI, các yêu cầu tính toán hiệu năng cao, ba xưởng đúc lớn, cũng như hệ sinh thái của họ, đang chạy đua trong việc tối ưu những gì họ đang có và phát triển những công nghệ hoàn toàn mới. Để hiện thực hóa được việc này, cần sự kết hợp giữa các tiêu chuẩn, các cách thức kết nối bên trong IC, đòi hỏi sự kết hợp đa ngành mà trước đây sự tương tác đó khá hạn chế nếu không muốn nói là không có.

Ví dụ, làm sao để đảm bảo ghép chính xác các chiplet không cùng công nghệ, đến từ những nhà sản xuất khác nhau lên cùng một khung. Rõ ràng là các nhà sản xuất từng là đối thủ không đội trời chung của nhau bây giờ cần phải ngồi lại với nhau. Cả ba ông lớn trên đều đang hoàn thiện kỹ thuật đóng gói này và phát triển mở rộng hệ sinh thái xung quanh nó.

Nguyễn Thanh Yên (Tổng Giám đốc Công ty Vi mạch CoAsia SEMI Việt Nam) dịch và tổng hợp

Tài liệu tham khảo

[1] https://www.chiphistory.org/505-moore-s-law-101-the-math-and-innovation-economics-behind-it

[2] https://irds.ieee.org/

[3] https://ictvietnam.vn/tich-hop-khong-dong-nhat-co-hoi-cho-phat-trien-linh-vuc-vi-mach-ban-dan-tai-viet-nam-23564.html

[4] https://www.semiconductors.org/resources/2015-international-technology-roadmap-for-semiconductors-itrs/

[5]https://semiengineering.com/intel-vs-samsung-vs-tsmc/

Chiplet là công nghệ sử dụng nhiều chip nhỏ (chiplet) kết nối lại với nhau để tạo thành một “bộ não” vi xử lý lớn hơn. Ngược lại với các chip truyền thống vốn tích hợp tất cả các thành phần trên một miếng silicon duy nhất, các chiplet có cách tiếp cận theo module. Mỗi chiplet là một module với chức năng riêng - như xử lý hoặc lưu trữ dữ liệu - sau đó, chúng được kết nối để trở thành một hệ thống.

Vì mỗi chiplet nhỏ và chuyên dụng hơn nên chi phí sản xuất chúng cũng rẻ hơn và ít có khả năng bị lỗi hơn. Đồng thời, người ta có thể nâng cấp từng chiplet để cải thiện hiệu suất, trong khi giữ nguyên các chiplet phụ trách chức năng khác.

Việc đảm bảo nhiều chiplet có thể cùng hoạt động cần đến các kỹ thuật đóng gói phức tạp hơn so với các kỹ thuật đóng gói chip đơn mảnh truyền thống. Công nghệ được sử dụng trong quy trình này được gọi là đóng gói tiên tiến.

Chiplet được tạp chí MIT Technology Review bình chọn là một trong 10 công nghệ đột phá của năm 2024. Các công ty lớn trong lĩnh vực chip như AMD, Intel và Apple đều sử dụng công nghệ này trong các sản phẩm của mình vì với họ, chiplet là một trong những cách mà ngành công nghiệp bán dẫn có thể tiếp tục tăng công suất tính toán của chip, bất chấp giới hạn vật lý.

|

Tin đăng số 1308 (số 36/2024) KH&PT